可编程逻辑器件设计及应用实验报告(DOC 33页)

所属分类:PLD可编程逻辑器件

文件大小:3324 KB

下载要求:10 学币或VIP

点击下载

精品资料网 >> 行业分类 >> PCB SMT PLD资料 >> PLD可编程逻辑器件 >> 资料信息

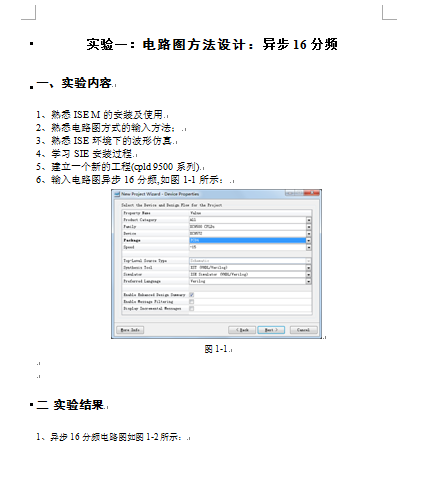

一、 实验内容

一、实验内容

一位全加器功能仿真结果:

三 实验结果讨论分析

串行通信:数据一位一位次序发送或接收。

二 实验结果

仿真波形设置如下:

仿真测试输入波形如下:

仿真结果如下:

可编程逻辑器件设计及应用

国际上规定的一个标准波特率系列:

图1-1

图1-2

图1-3

图1-4

图1-5

图2-1一位全加器

图2-2波形仿真激励

图2-3模块建立

图2-4 8位全加器(顶层电路图)

图2-5 8位全加器波形仿真激励

图2-6 功能仿真结果

图2-7 功能仿真结果

图2-8 功能仿真结果

图3-1 建立一个新的verilog模块

图3-2 输入全加器

图3-3 测试波形

图3-4 测试波形

图3-5 仿真测试结果

图3-6 仿真测试结果

图3-7 仿真测试结果

图3-8 仿真测试结果

图4-1 LED显示模块

图4-2 数据锁存模块

图4-3 顶层

图4-4 测试波形

图4-5 仿真结果

图4-6 测试波形

图4-7 仿真结果

图5-1 模式控制模块

图5-10 仿真结果

图5-11 测试波形设置

图5-12 仿真结果

图5-13 测试波形设置

图5-14 仿真结果

图5-15 测试波形设置

图5-16 仿真结果

图5-17 仿真结果

图5-18 顶层文件

图5-19 测试波形

图5-2 波特率发生模块

图5-20 测试波形

图5-21 仿真结果

图5-22 仿真结果

图5-3 发送数据模块

图5-4 发送数据模块

图5-5 测试波形设置

图5-6 仿真结果

图5-7 测试波形设置

图5-8 仿真结果

图5-9 测试波形设置

..............................

精品资料网 m.cnshu.cn

Copyright © 2004- 粤ICP备10098620号-1